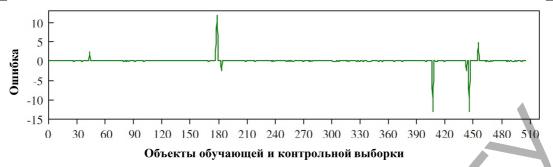

Рис. 9. Результаты экспериментальных исследований моделей с функциями принадлежности Гаусса

моделирования процессов по оценке сайтов. В рамках системы эффективно используются экспертная информация и строгие математические методы, правила типа Если-То легко поддаются пониманию и интерпретации.

Таким образом, использование математических моделей и методов в значительной степени сокращает количество средств и времени, необходимых для получения результатов при решении нетривиальной задачи по оценке сайтов.

## СПИСОК ЦИТИРОВАННЫХ ИСТОЧНИКОВ

- Lee, S. The effects of usability and web design attributes on user preference for e-commerce web sites / S. Lee, R.J. Koubek //Computers in Industry. – 2010. –Vol. 61(4). – P. 329–341.

- Liu Huan. Fuzzy analytic hierarchy process approach for E-Commerce websites evaluation / Huan Liu, V. Krasnoproshin, Shuang Zhang //World Scientific Proceedings Series on Computer Engineering and Information Science. – Spain: World Scientific, 2012. – Vol. 6. – P. 276–285.

- 3. Liu Huan. Algorithms for Evaluation and Selection E-Commerce Web-sites / Huan Liu, V. Krasnoproshin, Shuang Zhang //Journal of Computational Optimization in Economics and Finance. New York: USA, 2012. Vol. 4. № 2–3. P. 135–148.

- Liu Huan. Combined Method for E-Commerce Website Evaluation Based on Fuzzy Neural Network / Huan Liu, V. Krasnoproshin,

- Shuang Zhang //Applied Mechanics and Materials. 2013. Vol. 380. P. 2135–2138.

- Law R. Progress in tourism management: A review of website evaluation in tourism research / R. Law, S. Qi, D. Buhalis //Tourism Management. 2010 Vol. 31(3) P. 297–313.

- Hung W. Developing an evaluation instrument for e-commerce web sites from the first-time buyer's viewpoint / W. Hung, R. J. McQueen //Electron. J. Inform. Syst. Eval. – 2004. –Vol. 7(1) – P. 31–42.

- Azamathulla H. M. ANFIS-based approach for predicting sediment transport in clean sewer / H. M. Azamathulla, A. Ab Ghani, S. Y. Fei //Applied Soft Computing. 2012. Vol. 12(3) P. 1227–1230.

Dwivedi A.A Business Intelligence Technique for Forecasting the

- Dwivedi A.A Business Intelligence Technique for Forecasting the Automobile Sales using Adaptive Intelligent Systems (ANFIS and ANN) / A. Dwivedi, M. Niranjan, K. Sahu //International Journal of Computer Applications. – 2013. – Vol. 74(9). – P. 7–13.

- Jang J. S. R. ANFIS: Adaptive-network-based fuzzy inference systems / J. S. R. Jang //IEEE Transactions on Systems Man and Cybernetics. 1993. Vol. 23. P. 665–685.

- Petković D. Adaptive neuro-fuzzy estimation of conductive silicone rubber mechanical properties / D. Petković, M. Issa, N.D. Pavlović, et al. //Expert Systems with Applications. – 2012. –Vol. 39(10) – P. 9477–9482.

- Singh R. Estimation of elastic constant of rocks using an ANFIS approach / R. Singh, A. Kainthola, T.N. Singh //Applied Soft Computing. 2012. Vol. 12(1) P. 40–45.

Материал поступил в редакцию 19.11.13

### LIU HUAN Quality classification of commercial sites based on adaptive neural fuzzy inference system

This paper describes a combined approach to the quality classification problem of E-commerce sites, based on the use of the methodology of adaptive neural networks with fuzzy inference. A model of a neural network was proposed, in the frame of which expert fuzzy reasoning and rigorous mathematical methods were jointly used. The intelligent system with fuzzy inference was realized based on the model in Matlab software environment. It shows that the system is an effective tool for the quality analysis process modelling of the given type of sites.

УДК 004.31:004.312.44

# Черкасский Н.В., Ткачук Т.И.

# ПАРАМЕТРИЧЕСКАЯ ОПТИМИЗАЦИЯ УСТРОЙСТВА БПФ

Введение. Задачей работы является анализ устройства БПФ на 4х умножителях и проведения его параметрической оптимизации за характеристиками сложности, для построения эффективного конвейера. Примем за основу проектирования спецпроцессора Н-модель алгоритма [1] и характеристики сложности компьютерных алгоритмов.

**Н-модель алгоритма.** Н-модель алгоритма (H — Hardware) предназначена для синтеза, анализа и оптимизации комбинационных вычислительных средств. Возможность ее построения не противоречащей первой аксиоме компьютерных алгоритмов: алгоритм может быть реализован аппаратными средствами.

H – модель алгоритма – это пятерка: H: <A, Q,  $q_0$ ,  $q_f$ , G>; где A – конечное множество символов внешнего алфавита;

Q – конечное множество состояний H-модели;  $q_0$  і  $q_f$  – начальное и конечное состояния ( $q_0$ ,  $q_f \in Q$ );

G – конфигурация аппаратных средств модели: G = (X, U),

где X – множество элементарных преобразователей; U – множество соединений.

Структурный синтез бабочки БПФ. Ведущим алгоритмом систем обработки сигналов является «Быстрое Преобразование Фурье». Существует большое количество литературных источников, посвященных его совершенствованию. Главным направлением совершенствования является повышение производительности, которая достигается тремя способами: конвейеризацией, аппаратным выполнением алгоритма и использованием параллелизма.

**Черкасский Николай Вячеславович,** д.т.н., профессор кафедры СКС Национального университета "Львовская политехника", e-mail: cherkas3@gmail.com.

Ткачук Тарас Игоревич, ассистент кафедры СКС Национального университета "Львовская политехника", e-mail: tkachuk\_t@hotmail.com.

Рассмотрим пример проведения синтеза устройства БПФ. Для структурного синтеза Н-модели начальной точкой является алгоритм. Рассмотрим алгоритм БПФ, одним из вариантов которого является разбиение массива входных данных на подмассивы. Вычисление для четных и нечетных отсчетов имеет следующий вид:

$$X(k)=X_0(k)+W_N^k X_1(k);$$

(1)

$$X\left(k+\frac{N}{2}\right)=X_0\left(k\right)+W_N^kX_1\left(k\right),\tag{2}$$

где  $W_N=\mathrm{e}^{-jrac{2\pi}{N}}$  .

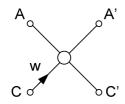

**Рис. 1.** «Бабочка» алгоритма БПФ

Графическое представление об алгоритме дает бабочка БПФ (рис. 1). Введем следующие обозначения переменных формулы БПФ:

$$A' = A + WC,$$

$$C' = A - WC.$$

(3)

Соответственно, в комплексной форме: A=a+jb; C=c+jd; W=w+jv.

$$A' = (a + cw - dv) + j(b + vc + dw), A' = (a - cw + dv) + j(b - (vc + dw)).$$

(4)

Проведем структурный синтез устройства БПФ по приведенным формулам. Для вычисления бабочки БПФ, нужно определить 4 переменные [2]: a' = a+cw-dv; b' = b+vc+dw; c' = a-(cw-dv); d' = b-(vc+dw).

Алгоритм БПФ предполагает выполнение двух основных операций – умножения и суммирования. Им в соответствие ставятся два устройства, устройство умножения и устройство суммирования. Каждый входной операнд используется при вычислениях дважды.

Исходя из теории SH-модели алгоритмов, в процессе структурного синтеза следует соблюдать следующие требования:

- минимизировать программную сложность, что позволяет уменьшить площадь кристалла, которую занимает устройство управления;

- использовать каноническую форму представления алгоритма, позволяет получить максимальную удельную производительность и минимальную структурную сложность.

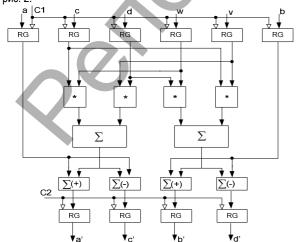

Схема, которая удовлетворяет этим требованиям, изображена на рис. 2.

**Рис. 2.** Схема устройства, которое реализует бабочку БПФ

Анализируя схему можно отметить, что организация загрузки входных данных в регистры достаточно проста, что не вызывает осложнения программной сложности. Устройством, который обладает наибольшей задержкой в этой схеме, является устройство умножения. Вычисление бабочки БПФ на данном устройстве выполняется за одно параллельное умножение.

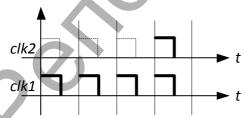

Для определения возможности оптимизации рассматриваемой схемы нужно провести анализ ее характеристик сложности. На рис. 3 изображена временная диаграмма рассматриваемого устройства БПФ.

**Рис. 3.** Временная диаграмма устройства БПФ

Анализируя временную диаграмму, видим, что программная сложность здесь обусловлена только синхронизацией подачи данных, а потому равна нулю.

Схеме присущ естественный параллелизм. Здесь есть два параллельных блока выполнения вычислений, каждый из которых состоит из двух умножителей, трех сумматоров и регистров, для получения входных данных и сохранения результатов вычислений.

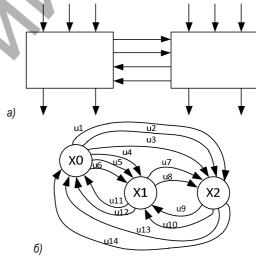

**Структурная сложность устройства.** Для проведения анализа структурной сложности построим блок-схему рассматриваемого устройства БПФ, объединив однородные части схемы в блоки (рис. 4a).

**Рис. 4.** а) блок схема б) граф-устройства БПФ с четырьмя устройствами умножения

Согласно Блок-схеме устройства строим граф работы устройства (рис. 4 б), где блоки схемы соответствуют узлам графа, в данном случае X1 и X2, а шины связей схемы — связями между узлами графа. В приведенном графе дополнительно изображен узел X0, отвечающий памяти устройства, то есть элемент, где хранятся исходные данные и передается результат работы устройства. Для вычислений структурной сложности построим матрицу инциденций графа (таблица 1).

Проведя необходимые расчеты, вычисляем структурную сложность [3] для рассматриваемого устройства БПФ. S = -28  $\log_2 28/42 \approx 16.8$ .

Параметрическая оптимизация. При проектировании таких аппаратно реализованных устройств отправным пунктом является требование: задержка шага конвейера не должна превышать задержки многоразрядного сумматора. Для выполнения такого требования воспользуемся устройством умножения с диагональным распространением переноса [3]. В таком устройстве умножения методом разделения известной схемы на две части и добавления конвейерных регистров, было получено быстродействие работы конвейера эквивалентно быстродействию работы многоразрядного сумматора.

**Таблица 1.** Матрица инциденций графа (рис. 4б)

| рица инциденции графа (рис. 40) |    |    |    |    |    |    |    |    |    |    |     |     |     |     |     |

|---------------------------------|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|

|                                 |    | u1 | u2 | u3 | u4 | u5 | u6 | u7 | u8 | u9 | u10 | u11 | u12 | u13 | u14 |

|                                 | X0 | 1  | 1  | 1  | 1  | 1  | 1  |    |    |    |     | -   | -   | -   | -   |

|                                 | X1 |    |    |    | -  | -  | -  | 1  | 1  | -  | -   | 1   | 1   |     |     |

|                                 | X2 | -  | -  | -  |    |    |    | -  | -  | 1  | 1   |     |     | 1   | 1   |

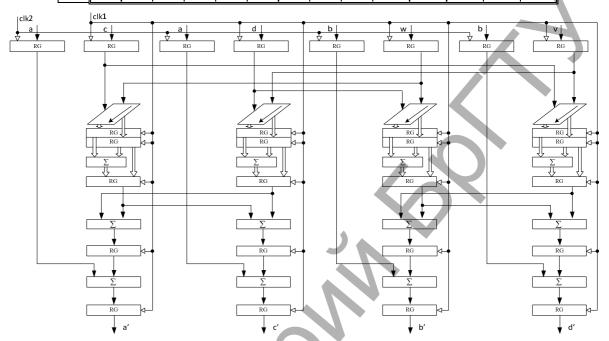

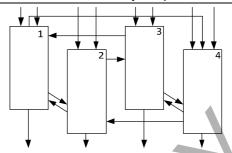

**Рис. 5.** Конвейерное устройство БПФ с разделением на 4 параллельных блока

На рисунке 5 показан оптимизированный вариант конвейерного устройства, выполняющего алгоритм бабочки БПФ. Управление операциями на сумматорах, сложение или вычитание выполняется с помощью сигналов управления, подаваемых на каждый сумматор.

Предыдущая схема, для удобства топологии проектирования, была разделена на 4 параллельные ветки выполнения алгоритма. Структурная сложность такого устройства будет другой, за счет незначительного увеличения аппаратной сложности и внешней структуры устройства мы достигли уменьшения структурной сложности внутри блоков. Такой вариант будет удобнее при создании прошивки ПЛИС. Нужно создать проект одного такого блока и просто продублировать его, правильно организовав соединение между блоками. На рис.6 изображена временная диаграмма оптимизированного устройства БПФ.

**Рис. 6.** Временная диаграмма оптимизированного устройства БПФ

Программная сложность здесь, как и в предыдущем случае, обусловлена только синхронизацией подачи входных данных, а потому остается нулевой.

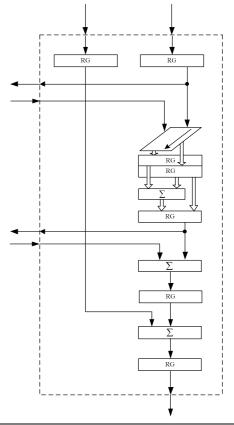

Схема одного блока изображена на рис. 7а. Такой блок значительно проще проектировать, по сравнению с первой схемой (рис. 2). Вариант разбиения схемы на 4 параллельных блока позволяет разместить ее на 4-х различных устройствах, если бы такая схема не уместилась по объему оборудования на один кристалл ПЛИС. На

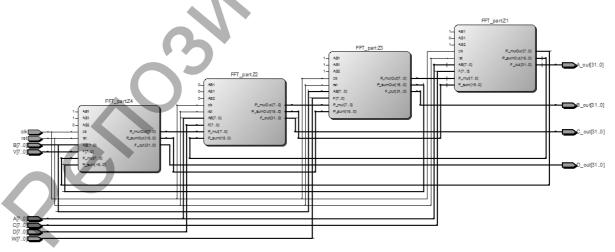

рис. 76 изображена блок-схема одного блока, которая была смоделирована в программе Quartus фирмы Altera.

**Puc. 7.** а) схема устройства б) смоделированная схема – одного блока конвейерного устройства БПФ

Теперь схема состоит из четырех одинаковых параллельных блоков, объединенных внешними связями (рис. 8).

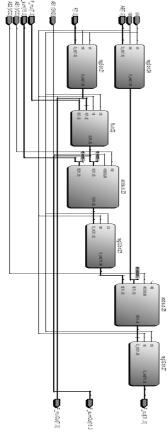

Анализ структурной сложности проводится на двух уровнях иерархии: одного блока (рис. 7а) и общей схемы устройства из четырех ветвей (рис. 8) S≈52,8. При проектировании на ПЛИС моделируемая схема будет иметь следующее представление (рис. 9).

**Рис. 8.** Блок-схема устройства БПФ, разделенного на 4 блока

#### Заключение

- Использование канонического выражения БПФ позволяет получить наибольшую удельную производительность по сравнению с другими устройствами БПФ.

- Структурная сложность представленного алгоритма БПФ с четырьмя устройствами умножения имеет минимальное значение.

- Представление схемы устройства БПФ на четырех умножителях в виде четырех блоков однородной структуры позволяет существенно упростить дальнейшие операции топологического проектирования схемы.

## СПИСОК ЦИТИРОВАННЫХ ИСТОЧНИКОВ

- Cherkaskyy Mykola, Murad Hussein Khalil, "H-Model of the Algorithm", Modern Problems of Radio Engineering, Telecommunications and Computer Science. Proceedings of the International Conference TCSET"2006. February 28 March 4, 2006, Lviv Slavsko, Ukraine. Lviv, Publishing House of Lviv Polytechnic, 2006. P. 44–45.

- Черкаський, М.В. Порівняння двох швидкодіючих структур / М.В. Черкаський, Т.І. Ткачук // Збірник матеріалів ІV міжвузівської науково-технічної конференції науково-педагогічних працівників "Проблеми та перспективи розвитку економіки і підприємництва та комп'ютерних технологій в Україні". (Львів, 30 березня 10 квітня 2009р). Львів: Видавничий відділ Інституту підприємництва та перспективних технологій, 2009. С. 230–231.

- Черкаський, М.В. Характеристики складності пристроїв множення / М.В. Черкаський, Т.І. Ткачук // Науково-технічний журнал «РАДІО-ЕЛЕКТРОННІ І КОМП'ЮТЕРНІ СИСТЕМИ» Національного аерокосмічного університету ім. М.Є. Жуковського, «Харківський авіаційний інститут». – 2012. – №5(57). – С. 142–147.

**Рис. 9.** Смоделированная схема устройства, БПФ разделенного на 4 блока

Материал поступил в редакцию 19.11.13

# CHERKASKYY N.V., TKACHUK T.I. Parametrical optimization of the BPF device

Considered the use of H-model for the synthesis of specialized functions, the advantages of pipelining and parallel structure of the canonical FFT algorithm are shown, was analyzed the complexity characteristics of the device.